DTL-Technik

Die DTL-Logik (DTL steht für Dioden-Transistor-Logik) ist eine Möglichkeit, die Einfachheit der Dioden-Logik mit der Transistortechnik zu kombinieren.

Blockschaltbild eines Logikgatters

Die eigentliche Logik wird durch mehrere Dioden

realisiert.

Die Ausgangsstufe besteht aus einem oder mehreren

Transistoren. Sie sorgt dafür, dass die Schaltung die Eingänge mehrerer nachfolgender

Logikgatter treiben kann.

Die Verwendung von Transistoren macht es außerdem möglich, Inverter zu bilden, die mit Dioden alleine nicht realisierbar sind.

Zwar ist die DTL-Technik veraltet, sie kann aber gut zum Verständnis der Elektronik, die hinter Logikschaltungen steckt, herangezogen werden. Die Schaltungen lassen sich einfach diskret aufbauen, beispielsweise auf dem Steckbrett, um dann ihre Eigenschaften vermessen zu können.

Um die Gatterlaufzeiten gering zu halten, sollten schnelle Schaltdioden verwendet werden. Durch die Verwendung von langsameren Dioden können die Auswirkungen von Gatterlaufzeiten auf die Funktion der Schaltung gut messtechnisch erfasst werden.

Programmierbare Logikbausteine basieren im Prinzip auf Diodenmatrizen, aus denen Grundgatter mit mehreren Eingängen gebildet werden.

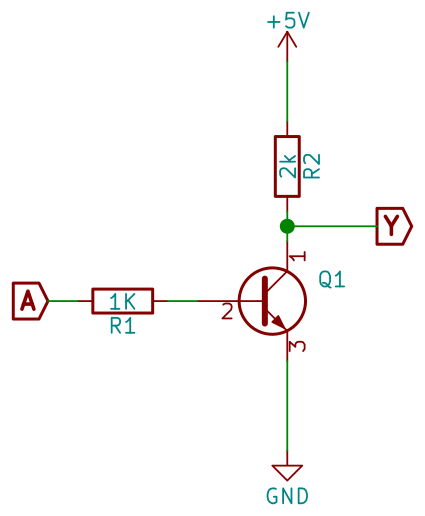

NICHT-Gatter in DTL-Technik

Aufbau

Das NICHT-Gatter in DTL-Technik besteht in seiner einfachsten

Form aus einem Transistor. Dieser invertiert das an seiner Basis anliegende Eingangssignal

A.

Dioden werden nicht eingesetzt, da diese nicht in der Lage sind, ein Signal zu invertieren.

NICHT-Gatter in DTL-Technik

Funktionsweise

-

Liegt ein LOW am Eingang A der Schaltung an, wird die Basis-Emitter-Schwellspannung UBE(on) des Transistors nicht überschritten. Der Transistor sperrt und am Ausgang Y liegt HIGH an.

-

Liegt ein HIGH am Eingang A der Schaltung an, wird die Basis-Emitter-Schwellspannung UBE(on) des Transistors überschritten. Der Transistor schaltet durch und am Ausgang Y liegt LOW an, weil der durchgeschaltete (niederohmige) Transistor den Ausgang gegen GND zieht.

Ein gravierender Nachteil dieser Schaltung ist, dass der Ausgangswiderstand abhängig vom Ausgangspegel ist. Bei HIGH-Pegel am Ausgang ist der Transistor gesperrt und der Ausgangswiderstand ergibt sich im Wesentlichen durch den Wert von R2.

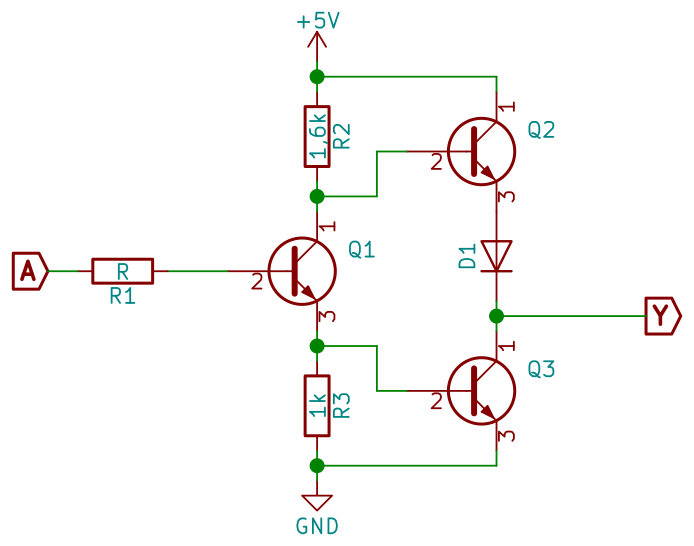

NICHT-Gatter mit Totem-Pole Endstufe

Den Nachteil der obigen Schaltung (pegelabhängiger Ausgangswiderstand) kompensiert man durch den Einsatz einer Gegentakt-Endstufe als Ausgangsverstärker. Diese Schaltung wird auch als Totem-Pole-Schaltung bezeichnet. Sie garantiert einen niedrigen Ausgangswiderstand gegen Masse und gegen die Betriebsspannung. Es können auch mehr nachfolgende Logikgatter angesteuert werden. Der erhöhte Bauteilebedarf fällt nicht ins Gewicht, da Logikgatter als integrierte Schaltungen (ICs) hergestellt werden.

NICHT-Gatter mit Totem-Pole-Endstufe

Link to the video in English language

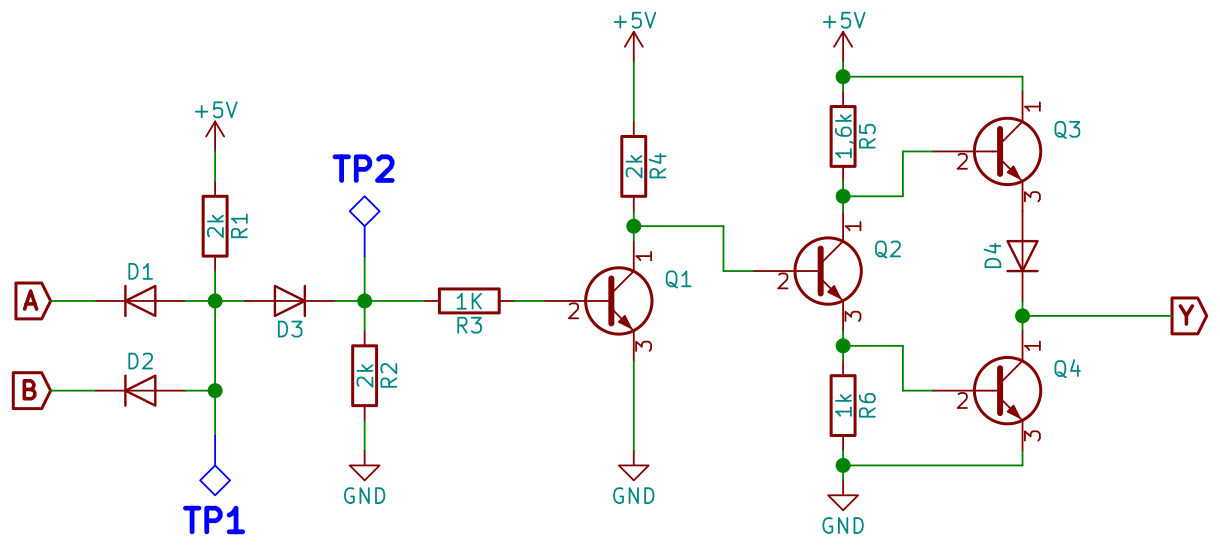

UND-Gatter in DTL-Technik

Aufbau

Die eigentliche Logik wird durch die Dioden D1-D3

realisiert.

Die Ausgangsstufe besteht aus den Transistoren Q1-Q4.

Sie sorgt dafür, dass die Schaltung die Eingänge mehrerer nachfolgender Logikgatter treiben kann.

UND-Gatter in DTL-Technik

Funktionsweise

-

Liegen beide Eingänge A und B auf HIGH, so fließt kein nennenswerter Strom durch die Dioden D1 und D2.

Die Spannung UTP1 am Testpunkt TP1 (bezogen auf GND) ergibt sich aus der Betriebsspannung abzüglich dem Spannungsabfall am Widerstand R1.

Die Spannung UTP2 am Testpunkt TP2 ist um die Flussspannung der Diode D3 niedriger als UTP1. UTP2.ist ausreichend hoch, um den nachfolgenden Transistor Q1 durchzuschalten.

Q1 invertiert das Signal. Die anschließende invertierende Totem-Pole Endstufe aus den Transistoren Q2-Q4 dient als Impedanzwandler.

Der Ausgang Y liegt dann auf HIGH. -

Liegt einer der Eingänge auf LOW, so ergibt sich UTP1 aus ULOW + der Flussspannung UF der Diode D1 bzw. D2.

Da UTP2=UTP1-UF ist, muss UTP2 dann auf LOW liegen.

Die beiden nachgeschalteten Verstärkerstufen sorgen dafür, dass der Ausgang Y ebenfalls auf LOW liegt.

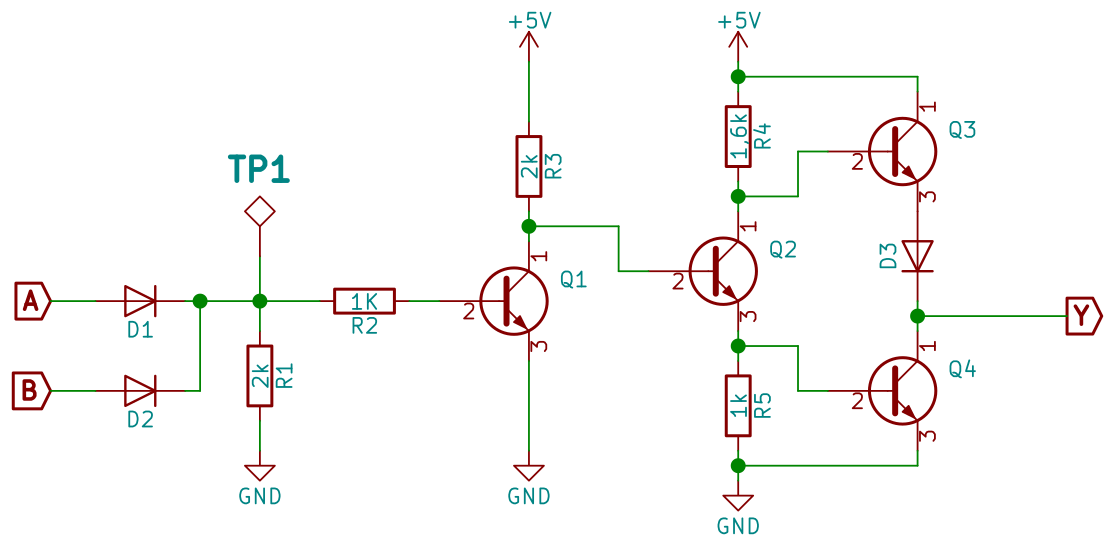

ODER-Gatter in DTL-Technik

Aufbau

Die eigentliche Logik wird durch die Dioden D1-D2

realisiert.

Die Ausgangsstufe besteht aus den Transistoren Q1-Q4.

Sie sorgt dafür, dass die Schaltung die Eingänge mehrerer nachfolgender Logikgatter treiben kann.

ODER-Gatter in DTL-Technik

Funktionsweise

-

Liegen beide Eingänge A und B auf LOW, so fließt kein nennenswerter Strom durch die Dioden D1 und D2.

Die Spannung UTP1 am Testpunkt TP1 (bezogen auf GND) wird durch den Widerstand R1 auf GND gezogen.

Der nachfolgende Transistor Q1 sperrt.

Q1 invertiert das Signal. Die anschließende invertierende Totem-Pole Endstufe aus den Transistoren Q2-Q4 dient als Impedanzwandler.

Der Ausgang Y liegt dann auf LOW. -

Liegt einer der Eingänge auf HIGH, reicht UTP1 aus, um den nachfolgenden Transistor Q1 durchzuschalten.

Die nachgeschaltete invertierende Verstärkerstufe sorgt dafür, dass der Ausgang Y ebenfalls auf HIGH liegt.